Intel 8080

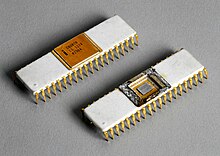

Closed and open Intel 8080 processor | |

| General information | |

|---|---|

| Launched | April 1974 |

| Discontinued | 1990[1] |

| Marketed by | Intel |

| Designed by | Intel |

| Common manufacturer |

|

| Performance | |

| Max. CPU clock rate | 2 MHz to 3.125 MHz |

| Data width | 8 bits |

| Address width | 16 bits |

| Architecture and classification | |

| Technology node | 6 μm |

| Instruction set | 8080 |

| Physical specifications | |

| Transistors |

|

| Cores |

|

| Package |

|

| Socket | |

| History | |

| Predecessor | Intel 8008 |

| Successor | Intel 8085 |

| Support status | |

| Unsupported | |

The Intel 8080 ("eighty-eighty") is the second 8-bit microprocessor designed and manufactured by Intel. It first appeared in April 1974 and is an extended and enhanced variant of the earlier 8008 design, although without binary compatibility.[3] The initial specified clock rate or frequency limit was 2 MHz, with common instructions using 4, 5, 7, 10, or 11 clock cycles. As a result, the processor is able to execute several hundred thousand instructions per second. Two faster variants, the 8080A-1 and 8080A-2, became available later with clock frequency limits of 3.125 MHz and 2.63 MHz respectively.[4] The 8080 needs two support chips to function in most applications: the i8224 clock generator/driver and the i8228 bus controller. The 8080 is implemented in N-type metal–oxide–semiconductor logic (NMOS) using non-saturated enhancement mode transistors as loads[5][6] thus demanding a +12 V and a −5 V voltage in addition to the main transistor–transistor logic (TTL) compatible +5 V.

Although earlier microprocessors were commonly used in mass-produced devices such as calculators, cash registers, computer terminals, industrial robots,[7] and other applications, the 8080 saw greater success in a wider set of applications, and is largely credited with starting the microcomputer industry.[8] Several factors contributed to its popularity: its 40-pin package made it easier to interface than the 18-pin 8008, and also made its data bus more efficient; its NMOS implementation gave it faster transistors than those of the P-type metal–oxide–semiconductor logic (PMOS) 8008, while also simplifying interfacing by making it TTL-compatible; a wider variety of support chips were available; its instruction set was enhanced over the 8008;[9] and its full 16-bit address bus (versus the 14-bit one of the 8008) enabled it to access 64 KB of memory, four times more than the 8008's range of 16 KB. It was used in the Altair 8800 and subsequent S-100 bus personal computers until it was replaced by the Z80 in this role, and was the original target CPU for CP/M operating systems developed by Gary Kildall.

The 8080 directly influenced the later x86 architecture. Intel designed the 8086 to have its assembly language be similar enough to the 8080, with most instructions mapping directly onto each other, that transpiled 8080 assembly code could be executed on the 8086.[10]

History

[edit]Microprocessor customers were reluctant to adopt the 8008 because of limitations such as the single addressing mode, low clock speed, low pin count, and small on-chip stack, which restricted the scale and complexity of software. There were several proposed designs for the 8080, ranging from simply adding stack instructions to the 8008 to a complete departure from all previous Intel architectures.[11] The final design was a compromise between the proposals.

Federico Faggin, the originator of the 8080 architecture in early 1972, proposed the chip to Intel's management and pushed for its implementation. He finally got the permission to develop it nine months later. Faggin hired Masatoshi Shima, who helped design the logic of the 4004 with him, from Japan in November 1972. Shima did the detailed design under Faggin's direction,[12] using the design methodology for random logic with silicon gate that Faggin had created for the 4000 family and the 8008.

The 8080 was explicitly designed to be a general-purpose microprocessor for a larger number of customers. Much of the development effort was spent trying to integrate the functionalities of the 8008's supplemental chips into one package. It was decided early in development that the 8080 was not to be binary-compatible with the 8008, instead opting for source compatibility once run through a transpiler, to allow new software to not be subject to the same restrictions as the 8008. For the same reason, as well as to expand the capabilities of stack-based routines and interrupts, the stack was moved to external memory.

Noting the specialized use of general-purpose registers by programmers in mainframe systems, Faggin with Shima and Stanley Mazor decided the 8080's registers would be specialized, with register pairs having a different set of uses.[13] This also allowed the engineers to more effectively use transistors for other purposes.

Shima finished the layout in August 1973. After the development of NMOS logic fabrication, a prototype of the 8080 was completed in January 1974. It had a flaw, in that driving with standard TTL devices increased the ground voltage because high current flowed into the narrow line. Intel had already produced 40,000 units of the 8080 at the direction of the sales section before Shima characterized the prototype. It was released as requiring Low-power Schottky TTL (LS TTL) devices. The 8080A fixed this flaw.[14]

Intel offered an instruction set simulator for the 8080 named INTERP/80 to run compiled PL/M programs. It was written in FORTRAN IV by Gary Kildall while he worked as a consultant for Intel.[15][16]

There is only one patent on the 8080 with the following names: Federico Faggin, Masatoshi Shima, Stanley Mazor.

Description

[edit]Programming model

[edit]

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 | (bit position) |

| Main registers | ||||||||||||||||

| A | Flags | Program Status Word | ||||||||||||||

| B | C | B | ||||||||||||||

| D | E | D | ||||||||||||||

| H | L | H (indirect address) | ||||||||||||||

| Index registers | ||||||||||||||||

| SP | Stack Pointer | |||||||||||||||

| Program counter | ||||||||||||||||

| PC | Program Counter | |||||||||||||||

| Status register | ||||||||||||||||

| S | Z | 0 | AC | 0 | P | 1 | C | Flags [17] | ||||||||

The Intel 8080 is the successor to the 8008. It uses the same basic instruction set and register model as the 8008, although it is neither source code compatible nor binary code compatible with its predecessor. Every instruction in the 8008 has an equivalent instruction in the 8080. The 8080 also adds 16-bit operations in its instruction set. Whereas the 8008 required the use of the HL register pair to indirectly access its 14-bit memory space, the 8080 added addressing modes to allow direct access to its full 16-bit memory space. The internal 7-level push-down call stack of the 8008 was replaced by a dedicated 16-bit stack-pointer (SP) register. The 8080's 40-pin DIP packaging permits it to provide a 16-bit address bus and an 8-bit data bus, enabling access to 64 KiB (216 bytes) of memory.

Registers

[edit]The processor has seven 8-bit registers (A, B, C, D, E, H, and L), where A is the primary 8-bit accumulator. The other six registers can be used as either individual 8-bit registers or in three 16-bit register pairs (BC, DE, and HL, referred to as B, D and H in Intel documents) depending on the particular instruction. Some instructions also enable the HL register pair to be used as a (limited) 16-bit accumulator. A pseudo-register M, which refers to the dereferenced memory location pointed to by HL, can be used almost anywhere other registers can be used. The 8080 has a 16-bit stack pointer to memory, replacing the 8008's internal stack, and a 16-bit program counter.

Flags

[edit]The processor maintains internal flag bits (a status register), which indicate the results of arithmetic and logical instructions. Only certain instructions affect the flags. The flags are:

- Sign (S), set if the result is negative.

- Zero (Z), set if the result is zero.

- Parity (P), set if the number of 1 bits in the result is even.

- Carry (C), set if the last addition operation resulted in a carry or if the last subtraction operation required a borrow.

- Auxiliary carry (AC or H), used for binary-coded decimal arithmetic (BCD).

The carry bit can be set or complemented by specific instructions. Conditional-branch instructions test the various flag status bits. The accumulator and the flags together are called the PSW, or program status word. PSW can be pushed to or popped from the stack.

Commands, instructions

[edit]As with many other 8-bit processors, all instructions are encoded in one byte (including register numbers, but excluding immediate data), for simplicity. Some can be followed by one or two bytes of data, which can be an immediate operand, a memory address, or a port number. Like more advanced processors, it has automatic CALL and RET instructions for multi-level procedure calls and returns (which can even be conditionally executed, like jumps) and instructions to save and restore any 16-bit register pair on the machine stack. Eight one-byte call instructions (RST) for subroutines exist at the fixed addresses 00h, 08h, 10h, ..., 38h. These are intended to be supplied by external hardware in order to invoke a corresponding interrupt service routine, but are also often employed as fast system calls. The instruction that executes slowest is XTHL, which is used for exchanging the register pair HL with the value stored at the address indicated by the stack pointer.

8-bit instructions

[edit]All 8-bit operations with two operands can only be performed on the 8-bit accumulator (the A register). The other operand can be either an immediate value, another 8-bit register, or a memory byte addressed by the 16-bit register pair HL. Increments and decrements can be performed on any 8 bit register or an HL-addressed memory byte. Direct copying is supported between any two 8-bit registers and between any 8-bit register and an HL-addressed memory byte. Due to the regular encoding of the MOV instruction (using a quarter of available opcode space), there are redundant codes to copy a register into itself (MOV B,B, for instance), which are of little use, except for delays. However, the systematic opcode for MOV M,M is instead used to encode the halt (HLT) instruction, halting execution until an external reset or interrupt occurs.

16-bit operations

[edit]Although the 8080 is generally an 8-bit processor, it has limited abilities to perform 16-bit operations. Any of the three 16-bit register pairs (BC, DE, or HL, referred to as B, D, H in Intel documents) or SP can be loaded with an immediate 16-bit value (using LXI), incremented or decremented (using INX and DCX), or added to HL (using DAD). By adding HL to itself, it is possible to achieve the same result as a 16-bit arithmetical left shift with one instruction. The only 16-bit instructions that affect any flag is DAD, which sets the CY (carry) flag in order to allow for programmed 24-bit or 32-bit arithmetic (or larger), needed to implement floating-point arithmetic. BC, DE, HL, or PSW can be copied to and from the stack using PUSH and POP. A stack frame can be allocated using DAD SP and SPHL. A branch to a computed pointer can be executed with PCHL. LHLD loads HL from directly addressed memory and SHLD stores HL likewise. The XCHG[18] instruction exchanges the values of the HL and DE register pairs. XTHLexchanges last item pushed on stack with HL.

Instruction set

[edit]| Opcode | Operands | Mnemonic | Clocks | Description | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | b2 | b3 | |||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | — | — | NOP | 4 | No operation |

| 0 | 0 | RP | 0 | 0 | 0 | 1 | datlo | dathi | LXI rp,data | 10 | RP ← data | |

| 0 | 0 | RP | 0 | 0 | 1 | 0 | — | — | STAX rp | 7 | (RP) ← A [BC or DE only] | |

| 0 | 0 | RP | 0 | 0 | 1 | 1 | — | — | INX rp | 5 | RP ← RP + 1 | |

| 0 | 0 | DDD | 1 | 0 | 0 | — | — | INR ddd | 5/10 | DDD ← DDD + 1 | ||

| 0 | 0 | DDD | 1 | 0 | 1 | — | — | DCR ddd | 5/10 | DDD ← DDD - 1 | ||

| 0 | 0 | DDD | 1 | 1 | 0 | data | — | MVI ddd,data | 7/10 | DDD ← data | ||

| 0 | 0 | RP | 1 | 0 | 0 | 1 | — | — | DAD rp | 10 | HL ← HL + RP | |

| 0 | 0 | RP | 1 | 0 | 1 | 0 | — | — | LDAX rp | 7 | A ← (RP) [BC or DE only] | |

| 0 | 0 | RP | 1 | 0 | 1 | 1 | — | — | DCX rp | 5 | RP ← RP - 1 | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | — | — | RLC | 4 | A1-7 ← A0-6; A0 ← Cy ← A7 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | — | — | RRC | 4 | A0-6 ← A1-7; A7 ← Cy ← A0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | — | — | RAL | 4 | A1-7 ← A0-6; Cy ← A7; A0 ← Cy |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | — | — | RAR | 4 | A0-6 ← A1-7; Cy ← A0; A7 ← Cy |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | addlo | addhi | SHLD add | 16 | (add) ← HL |

| 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | — | — | DAA | 4 | If A0-3 > 9 OR AC = 1 then A ← A + 6;

then if A4-7 > 9 OR Cy = 1 then A ← A + 0x60 |

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | addlo | addhi | LHLD add | 16 | HL ← (add) |

| 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | — | — | CMA | 4 | A ← ¬A |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | addlo | addhi | STA add | 13 | (add) ← A |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | — | — | STC | 4 | Cy ← 1 |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | addlo | addhi | LDA add | 13 | A ← (add) |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | — | — | CMC | 4 | Cy ← ¬Cy |

| 0 | 1 | DDD | SSS | — | — | MOV ddd,sss | 5/7 | DDD ← SSS | ||||

| 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | — | — | HLT | 7 | Halt |

| 1 | 0 | ALU | SSS | — | — | ADD ADC SUB SBB ANA XRA ORA CMP sss | 4/7 | A ← A [ALU operation] SSS | ||||

| 1 | 1 | CC | 0 | 0 | 0 | — | — | Rcc (RET conditional) | 5/11 | If cc true, PC ← (SP), SP ← SP + 2 | ||

| 1 | 1 | RP | 0 | 0 | 0 | 1 | — | — | POP rp | 10 | RP ← (SP), SP ← SP + 2 | |

| 1 | 1 | CC | 0 | 1 | 0 | addlo | addhi | Jcc add (JMP conditional) | 10 | If cc true, PC ← add | ||

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | addlo | addhi | JMP add | 10 | PC ← add |

| 1 | 1 | CC | 1 | 0 | 0 | addlo | addhi | Ccc add (CALL conditional) | 11/17 | If cc true, SP ← SP - 2, (SP) ← PC, PC ← add | ||

| 1 | 1 | RP | 0 | 1 | 0 | 1 | — | — | PUSH rp | 11 | SP ← SP - 2, (SP) ← RP | |

| 1 | 1 | ALU | 1 | 1 | 0 | data | — | ADI ACI SUI SBI ANI XRI ORI CPI data | 7 | A ← A [ALU operation] data | ||

| 1 | 1 | N | 1 | 1 | 1 | — | — | RST n | 11 | SP ← SP - 2, (SP) ← PC, PC ← N x 8 | ||

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | — | — | RET | 10 | PC ← (SP), SP ← SP + 2 |

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | addlo | addhi | CALL add | 17 | SP ← SP - 2, (SP) ← PC, PC ← add |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | port | — | OUT port | 10 | Port ← A |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | port | — | IN port | 10 | A ← Port |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | — | — | XTHL | 18 | HL ↔ (SP) |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | — | — | PCHL | 5 | PC ← HL |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | — | — | XCHG | 4 | HL ↔ DE |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | — | — | DI | 4 | Disable interrupts |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | — | — | SPHL | 5 | SP ← HL |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | — | — | EI | 4 | Enable interrupts |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | b2 | b3 | Mnemonic | Clocks | Description |

| SSS DDD | 2 | 1 | 0 | CC | ALU | RP | ||||||

| B | 0 | 0 | 0 | NZ | ADD ADI (A ← A + arg) | BC | ||||||

| C | 0 | 0 | 1 | Z | ADC ACI (A ← A + arg + Cy) | DE | ||||||

| D | 0 | 1 | 0 | NC | SUB SUI (A ← A - arg) | HL | ||||||

| E | 0 | 1 | 1 | C | SBB SBI (A ← A - arg - Cy) | SP or PSW | ||||||

| H | 1 | 0 | 0 | PO | ANA ANI (A ← A ∧ arg) | |||||||

| L | 1 | 0 | 1 | PE | XRA XRI (A ← A ⊻ arg) | |||||||

| M | 1 | 1 | 0 | P | ORA ORI (A ← A ∨ arg) | |||||||

| A | 1 | 1 | 1 | N | CMP CPI (A - arg) | |||||||

| SSS DDD | 2 | 1 | 0 | CC | ALU | |||||||

Input/output scheme

[edit]Input output port space

[edit]The 8080 supports up to 256 input/output (I/O) ports,[19] accessed via dedicated I/O instructions taking port addresses as operands.[20] This I/O mapping scheme is regarded as an advantage, as it frees up the processor's limited address space. Many CPU architectures instead use so-called memory-mapped I/O (MMIO), in which a common address space is used for both RAM and peripheral chips. This removes the need for dedicated I/O instructions, although a drawback in such designs may be that special hardware must be used to insert wait states, as peripherals are often slower than memory. However, in some simple 8080 computers, I/O is indeed addressed as if they were memory cells, "memory-mapped", leaving the I/O commands unused. I/O addressing can also sometimes employ the fact that the processor outputs the same 8-bit port address to both the lower and the higher address byte (i.e., IN 05h would put the address 0505h on the 16-bit address bus). Similar I/O-port schemes are used in the backward-compatible Zilog Z80 and Intel 8085, and the closely related x86 microprocessor families.

Separate stack space

[edit]One of the bits in the processor state word (see below) indicates that the processor is accessing data from the stack. Using this signal, it is possible to implement a separate stack memory space. This feature is seldom used.

Status word

[edit]For more advanced systems, during the beginning of each machine cycle, the processor places an eight bit status word on the data bus. This byte contains flags that determine whether the memory or I/O port is accessed and whether it is necessary to handle an interrupt.

The interrupt system state (enabled or disabled) is also output on a separate pin. For simple systems, where the interrupts are not used, it is possible to find cases where this pin is used as an additional single-bit output port (the popular Radio-86RK computer made in the Soviet Union, for instance).

Example code

[edit]The following 8080/8085 assembler source code is for a subroutine named memcpy that copies a block of data bytes of a given size from one location to another. The data block is copied one byte at a time, and the data movement and looping logic utilizes 16-bit operations.

1000 1000 1000 78 1001 B1 1002 C8 1003 1A 1004 77 1005 13 1006 23 1007 0B 1008 78 1009 B1 100A C2 03 10 100D C9 |

; memcpy --

; Copy a block of memory from one location to another.

;

; Entry registers

; BC - Number of bytes to copy

; DE - Address of source data block

; HL - Address of target data block

;

; Return registers

; BC - Zero

org 1000h ;Origin at 1000h

memcpy public

mov a,b ;Copy register B to register A

ora c ;Bitwise OR of A and C into register A

rz ;Return if the zero-flag is set high.

loop: ldax d ;Load A from the address pointed by DE

mov m,a ;Store A into the address pointed by HL

inx d ;Increment DE

inx h ;Increment HL

dcx b ;Decrement BC (does not affect Flags)

mov a,b ;Copy B to A (so as to compare BC with zero)

ora c ;A = A | C (are both B and C zero?)

jnz loop ;Jump to 'loop:' if the zero-flag is not set.

ret ;Return

|

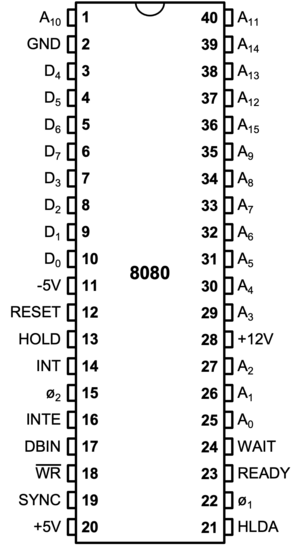

Pin use

[edit]

The address bus has its own 16 pins, and the data bus has 8 pins that are usable without any multiplexing. Using the two additional pins (read and write signals), it is possible to assemble simple microprocessor devices very easily. Only the separate IO space, interrupts, and DMA need added chips to decode the processor pin signals. However, the pin load capacity is limited; even simple computers often require bus amplifiers.

The processor needs three power sources (−5, +5, and +12 V) and two non-overlapping high-amplitude synchronizing signals. However, at least the late Soviet version КР580ВМ80А was able to work with a single +5 V power source, the +12 V pin being connected to +5 V and the −5 V pin to ground.

The pin-out table, from the chip's accompanying documentation, describes the pins as follows:

| Pin number | Signal | Type | Comment |

|---|---|---|---|

| 1 | A10 | Output | Address bus 10 |

| 2 | GND | — | Ground |

| 3 | D4 | Bidirectional | Bidirectional data bus. The processor also transiently sets here the "processor state", providing information about what the processor is currently doing:

|

| 4 | D5 | ||

| 5 | D6 | ||

| 6 | D7 | ||

| 7 | D3 | ||

| 8 | D2 | ||

| 9 | D1 | ||

| 10 | D0 | ||

| 11 | −5 V | — | The −5 V power supply. This must be the first power source connected and the last disconnected, otherwise the processor will be damaged. |

| 12 | RESET | Input | Reset. This active low signal forces execution of commands located at address 0000. The content of other processor registers is not modified. |

| 13 | HOLD | Input | Direct memory access request. The processor is requested to switch the data and address bus to the high impedance ("disconnected") state. |

| 14 | INT | Input | Interrupt request |

| 15 | φ2 | Input | The second phase of the clock generator signal |

| 16 | INTE | Output | The processor has two commands for setting 0 or 1 level on this pin. The pin normally is supposed to be used for interrupt control. However, in simple computers it was sometimes used as a single bit output port for various purposes. |

| 17 | DBIN | Output | Read (the processor reads from memory or input port) |

| 18 | WR | Output | Write (the processor writes to memory or output port). This is an active low output. |

| 19 | SYNC | Output | Active level indicates that the processor has put the "state word" on the data bus. The various bits of this state word provide added information to support the separate address and memory spaces, interrupts, and direct memory access. This signal is required to pass through additional logic before it can be used to write the processor state word from the data bus into some external register, e.g., 8238 Archived September 18, 2023, at the Wayback Machine-System Controller and Bus Driver. |

| 20 | +5 V | — | The + 5 V power supply |

| 21 | HLDA | Output | Direct memory access confirmation. The processor switches data and address pins into the high impedance state, allowing another device to manipulate the bus |

| 22 | φ1 | Input | The first phase of the clock generator signal |

| 23 | READY | Input | Wait. With this signal it is possible to suspend the processor's work. It is also used to support the hardware-based step-by step debugging mode. |

| 24 | WAIT | Output | Wait (indicates that the processor is in the waiting state) |

| 25 | A0 | Output | Address bus |

| 26 | A1 | ||

| 27 | A2 | ||

| 28 | 12 V | — | The +12 V power supply. This must be the last connected and first disconnected power source. |

| 29 | A3 | Output | The address bus; can switch into high impedance state on demand |

| 30 | A4 | ||

| 31 | A5 | ||

| 32 | A6 | ||

| 33 | A7 | ||

| 34 | A8 | ||

| 35 | A9 | ||

| 36 | A15 | ||

| 37 | A12 | ||

| 38 | A13 | ||

| 39 | A14 | ||

| 40 | A11 |

Support chips

[edit]A key factor in the success of the 8080 was the broad range of support chips available, providing serial communications, counter/timing, input/output, direct memory access, and programmable interrupt control amongst other functions:

- 8214 - Priority Interrupt Control Unit[21][22]

- 8224 – Clock generator

- 8228/8238 Archived September 18, 2023, at the Wayback Machine – System controller and bus driver

- 8251 – Communication controller

- 8253 – Programmable interval timer

- 8255 – Programmable peripheral interface

- 8257 – DMA controller

- 8259 – Programmable interrupt controller

Physical implementation

[edit]The 8080 integrated circuit uses non-saturated enhancement-load nMOS gates, demanding extra voltages (for the load-gate bias). It was manufactured in a silicon gate process using a minimal feature size of 6 μm. A single layer of metal is used to interconnect the approximately 4,500 transistors[23] in the design, but the higher resistance polysilicon layer, which required higher voltage for some interconnects, is implemented with transistor gates. The die size is approximately 20 mm2.

Commercial impact

[edit]Applications and successors

[edit]The 8080 is used in many early microcomputers, such as the MITS Altair 8800 Computer, Processor Technology SOL-20 Terminal Computer and IMSAI 8080 Microcomputer, forming the basis for machines running the CP/M operating system (the later, almost fully compatible and more able, Zilog Z80 processor would capitalize on this, with Z80 and CP/M becoming the dominant CPU and OS combination of the period c. 1976 to 1983 much as did the x86 and DOS for the PC a decade later).

In 1979, even after the introduction of the Z80 and 8085 processors, five manufacturers of the 8080 were selling an estimated 500,000 units per month at a price around $3 to $4 each.[24]

The first single-board microcomputers, such as MYCRO-1 and the dyna-micro / MMD-1 (see: Single-board computer) were based on the Intel 8080. One of the early uses of the 8080 was made in the late 1970s by Cubic-Western Data of San Diego, California, in its Automated Fare Collection Systems custom designed for mass transit systems around the world. An early industrial use of the 8080 is as the "brain" of the DatagraphiX Auto-COM (Computer Output Microfiche) line of products which takes large amounts of user data from reel-to-reel tape and images it onto microfiche. The Auto-COM instruments also include an entire automated film cutting, processing, washing, and drying sub-system.

Several early video arcade games were built around the 8080 microprocessor. The first commercially-available arcade video game to incorporate a microprocessor was Gun Fight, Midway Games' 8080-based reimplementation of Taito's discrete-logic Western Gun, which was released in November 1975.[25][26][27][28] (A pinball machine which incorporated a Motorola 6800 processor, The Spirit of '76, had already been released the previous month.[29][30]) The 8080 was then used in later Midway arcade video games[31] and in Taito's 1978 Space Invaders, one of the most successful and well-known of all arcade video games.[32][33]

Zilog introduced the Z80, which has a compatible machine language instruction set and initially used the same assembly language as the 8080, but for legal reasons, Zilog developed a syntactically-different (but code compatible) alternative assembly language for the Z80. At Intel, the 8080 was followed by the compatible and electrically more elegant 8085.

Later, Intel issued the assembly-language compatible (but not binary-compatible) 16-bit 8086 and then the 8/16-bit 8088, which was selected by IBM for its new PC to be launched in 1981. Later NEC made the NEC V20 (an 8088 clone with Intel 80186 instruction set compatibility) which also supports an 8080 emulation mode. This is also supported by NEC's V30 (a similarly enhanced 8086 clone). Thus, the 8080, via its instruction set architecture (ISA), made a lasting impact on computer history.

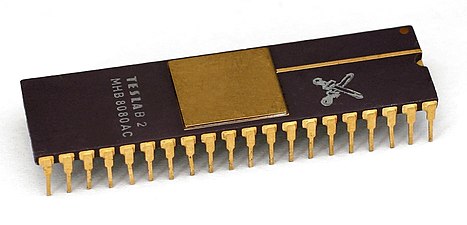

A number of processors compatible with the Intel 8080A were manufactured in the Eastern Bloc: the KR580VM80A (initially marked as КР580ИК80) in the Soviet Union, the MCY7880[34] made by Unitra CEMI in Poland, the MHB8080A[35] made by TESLA in Czechoslovakia, the 8080APC[35] made by Tungsram / MEV in Hungary, and the MMN8080[35] made by Microelectronica Bucharest in Romania.

As of 2017[update], the 8080 is still in production at Lansdale Semiconductors.[36]

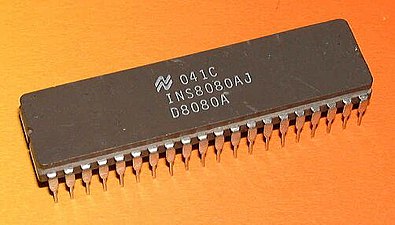

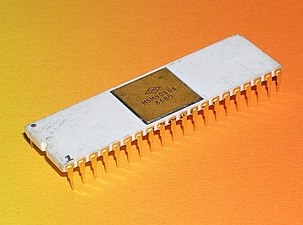

- Intel 8080 second sources

-

CEMI MCY7880 (Poland)

-

Kvazar Kiev K580IK80 (Soviet Union)

-

Mitsubishi Electric M5L8080

-

National Semiconductor INS8080

-

OKI MSM8080

-

Siemens SAB8080

-

Signetics MP8080

-

Tesla MHB8080

-

Texas Instruments TMS8080

-

5G8080 (PR China)

Industry change

[edit]This section possibly contains original research. (August 2017) |

The 8080 also changed how computers were created. When the 8080 was introduced, computer systems were usually created by computer manufacturers such as Digital Equipment Corporation, Hewlett-Packard, or IBM. A manufacturer would produce the whole computer, including processor, terminals, and system software such as compilers and operating system. The 8080 was designed for almost any application except a complete computer system. Hewlett-Packard developed the HP 2640 series of smart terminals around the 8080. The HP 2647 is a terminal which runs the programming language BASIC on the 8080. Microsoft's founding product, Microsoft BASIC, was originally programmed for the 8080.

The 8080 and 8085 gave rise to the 8086, which was designed as a source code compatible, albeit not binary compatible, extension of the 8080.[37] This design, in turn, later spawned the x86 family of chips, which continue to be Intel's primary line of processors. Many of the 8080's core machine instructions and concepts survive in the widespread x86 platform. Examples include the registers named A, B, C, and D and many of the flags used to control conditional jumps. 8080 assembly code can still be directly translated into x86 instructions,[vague] since all of its core elements are still present.

Cultural impact

[edit]- Asteroid 8080 Intel is named as a pun[citation needed] and praise on the name of Intel 8080.[38]

- Microsoft's published phone number, 425-882-8080, was chosen because much early work was on this chip.

- Many of Intel's main phone numbers also take a similar form: xxx-xxx-8080

See also

[edit]- CP/M – operating system

- S-100 bus

- MPT8080

- Intellec 8 Mod 80

- MDS 800

References

[edit]- ^ "CPU History – The CPU Museum – Life Cycle of the CPU". Archived from the original on January 16, 2010.

- ^ Lewnes, Ann, "The Intel386 Architecture Here to Stay", Intel Corporation, Microcomputer Solutions, July/August 1989, page 2

- ^ "From CPU to software, the 8080 Microcomputer is here". Electronic News. New York: Fairchild Publications. April 15, 1974. pp. 44–45. Electronic News was a weekly trade newspaper. The same advertisement appeared in the May 2, 1974, issue of Electronics magazine.

- ^ "8080A/8080A-1/8080A-2 8-Bit N Channel Microprocessor" (PDF). Intel. Archived (PDF) from the original on November 15, 2021. Retrieved November 16, 2021.

- ^ similar to pull-up resistors

- ^ Tohya, Hirokazu (2013). Switching Mode Circuit Analysis and Design: Innovative Methodology by Novel Solitary Electromagnetic Wave Theory. Bentham Science Publishers. p. 4. ISBN 9781608054497. Archived from the original on November 15, 2021. Retrieved November 28, 2020.

- ^ The 8008 (1972) was used for interpolation and control in ASEA's (now ABB) first line of general industrial robots, introduced October 1973.

- ^ Mueller, Scott (2006). Upgrading and Repairing PCs (17th ed.). Pearson Education. p. 37. ISBN 978-0-7897-3404-4. Archived from the original on November 16, 2021. Retrieved November 16, 2021.

- ^ The enhancements were largely based on customer feedback and Federico Faggin and others listening to minicomputer-oriented professionals about certain problems and lack of features in the 8008 architecture. (Source: 8008 and 8080 oral histories.)

- ^ Mazor, Stanley (June 1978). "The Intel 8086 Microprocessor: a 16-bit Evolution of the 8080". IEEE Computer. 11 (6): 18–27. doi:10.1109/C-M.1978.218219. S2CID 16962774. Archived from the original on September 19, 2021. Retrieved November 18, 2021.

- ^ Miller, Michael. "Creating the 8080: The Processor That Started the PC Revolution". PCMag. Zaff Davis. Archived from the original on November 14, 2021. Retrieved November 14, 2021.

- ^ Faggin, Federico. "8008 and 8080 Q&A". Microprocessor Intel 4004. Archived from the original on November 15, 2021. Retrieved November 15, 2021.

- ^ Mazor, Stanley (April–June 2007). "Intel 8080 CPU Chip Development". IEEE Annals of the History of Computing. 29 (2): 70–73. doi:10.1109/MAHC.2007.25. S2CID 14755544.

- ^ Shima, Masatoshi; Nishimura, Hirohiko; Ishida, Haruhisa (1979). "座談会 マイクロコンピュータの誕生 開発者 嶋 正利氏に聞く". Bit (in Japanese). 11 (11). 共立出版: 4–12. ISSN 0385-6984.

- ^ Kildall, Gary Arlen (June 27, 1974). "High-level language simplifies microcomputer programming" (PDF). Electronics. McGraw-Hill Education. pp. 103–109 [108]. Archived (PDF) from the original on November 14, 2021. Retrieved November 14, 2021.

- ^ "8080 Simulator INTERP/80" (PDF). Microcomputer Software. Intel Corporation. March 1975. Product Code 98-119A. MCS-516-0375/27.5K. Archived (PDF) from the original on November 25, 2023. Retrieved November 25, 2023. (2 pages)

- ^ 8080 Assembly Language Programming Manual (PDF) (Rev B ed.). Intel. 1975. p. 22. Retrieved February 29, 2024.

- ^ 8080 instruction encoding Archived March 5, 2018, at the Wayback Machine. ClassicCMP.org. Retrieved on October 23, 2011.

- ^ Note: Some Intel datasheets from the 1970s advertise 512 I/O ports, because they count input and output ports separately.

- ^ HAYES, JOHN P. (1978). Computer Architecture and Organization. McGraw-Hill. pp. 420–423. ISBN 0-07-027363-4.

- ^ Intel Corporation, "8214 Priorty Interrupt Control Unit", Intel 8080 Microcomputer Systems User's Manual, September 1975, page 5-153 Archived May 28, 2024, at the Wayback Machine from bitsaver.org in PDF

- ^ Intel Corporation, "Two Low-Cost, Programmable LSI Device Make Designs Easier To Implement, Reduce Cost Of 4-bit MCS-40 Systems", Intel Microcomputer News, Volume 3, No. 1, January 1976, page 1

- ^ "Intel Chips timeline" (PDF). Intel. Intel Corporation. Archived (PDF) from the original on November 14, 2021. Retrieved November 14, 2021.

- ^ Libes, Sol (November 1979). "Byte News". Byte. 11. Vol. 4. p. 82. ISSN 0360-5280.

- ^ "What was the first arcade game to use a microprocessor instead of discrete logic?". Archived from the original on April 11, 2023. Retrieved April 11, 2023.

- ^ Steve L. Kent (2001), The ultimate history of video games: from Pong to Pokémon and beyond : the story behind the craze that touched our lives and changed the world, p. 64, Prima, ISBN 0-7615-3643-4

- ^ Akagi, Masumi (October 13, 2006). アーケードTVゲームリスト国内•海外編(1971–2005) [Arcade TV Game List: Domestic • Overseas Edition (1971–2005)] (in Japanese). Japan: Amusement News Agency. p. 124. ISBN 978-4990251215.

- ^ "Dave Needle and Jerry Lawson - Two Early Independent Video Game Designers". July 29, 2013. Archived from the original on April 11, 2023. Retrieved April 11, 2023.

- ^ "Internet Pinball Machine Database: Mirco Games, Inc. 'Spirit of 76'". www.ipdb.org. Archived from the original on April 16, 2023. Retrieved April 11, 2023.

- ^ wayout440. "Mirco Spirit of 76 for sale – THE first solid state pin?". Pinside.com. Archived from the original on April 11, 2023. Retrieved April 11, 2023.

{{cite web}}: CS1 maint: numeric names: authors list (link) - ^ "Midway 8080 System Boards". Archived from the original on April 11, 2023. Retrieved April 11, 2023.

- ^ "Space Invaders Videogame by Bally Midway (1978)". Killer List of Videogames. Archived from the original on November 25, 2010. Retrieved April 11, 2023.

- ^ Edwards, Benj. "Ten Things Everyone Should Know About Space Invaders". 1UP.com. Archived from the original on February 26, 2009. Retrieved April 11, 2023.

- ^ MCY7880—a Polish-made clone of 8080 Archived August 17, 2016, at the Wayback Machine. CPU World. Retrieved on October 23, 2011.

- ^ a b c Soviet chips and their western analogs Archived February 9, 2017, at the Wayback Machine. CPU-world. Retrieved on October 23, 2011.

- ^ "Intel – Microprocessor 8080A Family & 828X Series". Lansdale Semiconductor Inc. Archived from the original on October 14, 2015. Retrieved June 20, 2017.

- ^ Morse, Stephen; Ravenel, Bruce; Mazor, Stanley; Pohlman, William (October 1980). "Intel Microprocessors: 8008 to 8086" (PDF). IEEE Computer. 13 (10): 42–60. doi:10.1109/MC.1980.1653375. S2CID 206445851. Archived (PDF) from the original on September 14, 2021. Retrieved November 5, 2021.

- ^ "(8080) Intel = 1958 QC = 1987 WU2 = 1989 AS5". Minor Planet Center. International Astronomical Union. Archived from the original on September 25, 2019. Retrieved November 14, 2021.

Further reading

[edit]- Leventhal, Lance (1978). 8080A/8085 Assembly Language Programming (1st ed.). Adam Osborne & Associates.[dead link]; 495 pages

- Miller, Alan (1981). 8080/Z80 Assembly Language – Techniques for Improved Programming (1st ed.). John Wiley & Sons. ISBN 978-0471081241.; 332 pages

- Zaks, Rodnay; Lesea, Austin (1979). Microprocessor Interfacing Techniques (3rd ed.). Sybex. ISBN 978-0-89588-029-1.; 466 pages

- Spracklen, Kathe (1979). Z80 and 8080 Assembly Language Programming (1st ed.). Hayden. ISBN 978-0810451674.; 180 pages

External links

[edit]- Intel and other manufacturers' 8080 CPU images and descriptions at cpu-collection.de Archived October 11, 2006, at the Wayback Machine

- Scan of the Intel 8080 data book at DataSheetArchive.com

- Microcomputer Design, Second Edition, 1976 Archived March 11, 2012, at the Wayback Machine

- 8080 Emulator written in JavaScript Archived March 17, 2010, at the Wayback Machine

- Intel 8080/KR580VM80A emulator in JavaScript Archived June 11, 2018, at the Wayback Machine

- Intel 8080 Microcomputer Systems User's Manual (September 1975, 262 pages) Archived March 10, 2018, at the Wayback Machine

- Intel 8080 Microcomputer Systems User's Manual (September 1975, 234 pages) Archived February 26, 2013, at the Wayback Machine

- Intel 8080/8085 Instruction Reference Card Archived August 10, 2021, at the Wayback Machine

Patent on 8080

[edit]- US patent 4010449, Federico Faggin, Masatoshi Shima, Stanley Mazor, "MOS computer employing a plurality of separate chips", issued March 1, 1977 This patent contain three claims. The first two relate to the status word multiplexed onto the data bus. The third claim is for the

RST 7instruction which can be invoked by pulling the data bus high. The prior art 8008RST 7required more complicated instruction jamming circuitry.